ARM架构凭借其低功耗、高性能及广泛的市场覆盖,已成为移动端和嵌入式设备AI计算的核心载体,神经网络算法在ARM平台上的高效实现,需结合硬件架构特性与算法优化策略,以平衡精度、速度与资源消耗,以下从核心技术、优化路径、应用场景及挑战等方面展开分析。

ARM神经网络算法的核心技术

ARM神经网络算法的实现依赖“硬件+软件”协同优化体系,硬件层面,ARM推出的Ethos系列NPU(神经网络处理器)是关键,其通过脉动阵列(Systolic Array)架构高效加速矩阵乘法、卷积等核心运算,支持INT8/INT16量化计算,能效比比通用CPU提升10-100倍,Ethos-U55 microNPU专为微控制器设计,算力达0.5 TOPS,功耗仅数毫瓦,可部署在可穿戴设备、传感器等资源受限场景。

软件层面,ARM提供全栈工具链:CMSIS-NN是轻量级神经网络内核库,针对ARM Cortex-M/Cortex-A系列优化,支持CNN、RNN等常用网络;ARM Compute Library(ACL)则面向高端设备,提供CPU+GPU+NPU异构计算调度能力,兼容TensorFlow Lite、PyTorch Mobile等框架,简化模型部署流程,ARM AI生态还包含工具如Arm NN,用于跨框架模型转换,确保开发者能在不同硬件上复用算法代码。

神经网络算法在ARM平台的优化策略

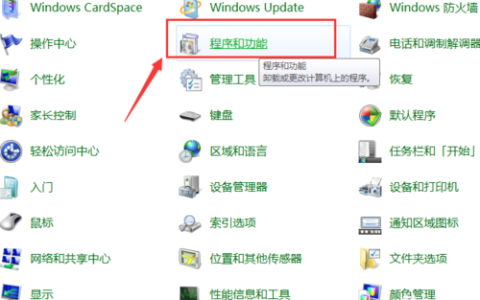

受限于移动端算力与内存,神经网络算法需从模型、计算、数据三维度优化。模型优化主要采用量化(Quantization)与压缩技术:量化将FP32模型转为INT8/INT4,精度损失通常低于1%,但计算速度提升2-4倍,内存占用减少50%以上;剪枝(Pruning)通过移除冗余神经元或连接,减少模型参数量,如MobileNetV3剪枝后体积缩小60%,仍保持95%以上精度。计算优化则聚焦内存访问与并行化:通过Winograd算法将卷积运算转换为矩阵乘法,减少计算量;利用ARM NEON SIMD指令集实现数据并行处理,加速激活函数(如ReLU)、池化等操作。数据优化涉及内存对齐与缓存重用,通过数据重排(如NHWC→NCHW)提升缓存命中率,减少数据搬运延迟。

以下为不同优化策略的效果对比:

| 优化策略 | 精度损失 | 计算加速比 | 内存占用降低 | 适用场景 |

|—————-|———-|————|————–|————————|

| INT8量化 | <1% | 2-4x | 50%+ | 移动端图像分类、语音识别 |

| 结构化剪枝 | 1-3% | 3-5x | 60%+ | 实时目标检测、分割 |

| 知识蒸馏 | <2% | 2-3x | 40%+ | 大模型轻量化(如BERT) |

应用场景与挑战

ARM神经网络算法已广泛渗透消费电子、工业、车载等领域,在智能手机中,AI摄影(如实时虚化、夜景降噪)依赖ARM NPU加速的CNN模型;可穿戴设备通过Cortex-M系列与CMSIS-NN实现心率异常检测等健康算法;工业端,基于Ethos-U的边缘节点可实时分析生产线缺陷,响应延迟<10ms。

当前挑战主要集中在三方面:一是模型复杂度与硬件资源的矛盾,如Transformer模型在微控制器上部署仍显臃肿;二是异构计算开发门槛高,需开发者熟悉CPU+GPU+NPU协同逻辑;三是安全隐私问题,端侧模型易受逆向工程攻击,需结合硬件级加密(如ARM TrustZone)保护数据,随着ARM架构持续迭代(如Cortex-A78AE支持混合精度计算)与AI编译器优化(如自动算子融合),ARM神经网络算法将在更广泛的边缘场景实现“高效智能”。

FAQs

Q1:ARM神经网络算法与PC端算法的主要区别是什么?

A1:区别主要体现在硬件适配与优化目标上,PC端(如x86+GPU)侧重高算力,支持FP32/FP16精度,模型体积大;ARM端受限于低功耗与内存,需通过量化、剪枝等手段压缩模型,优先支持INT8/INT4,强调实时性与能效比,ARM端依赖专用NPU与轻量级软件栈(如CMSIS-NN),而PC端更多依托CUDA、ROCm等通用并行计算框架。

Q2:如何在ARM设备上选择神经网络优化策略?

A2:选择需结合硬件资源与任务需求:若设备为高端手机(如Cortex-A系列+NPU),可优先用INT8量化+异构计算,平衡精度与速度;若为微控制器(如Cortex-M系列),需采用轻量模型(如MobileNet)+结构化剪枝,并依赖CMSIS-NN实现极致优化;对于实时性要求高的场景(如自动驾驶),可结合模型蒸馏与硬件加速器,确保低延迟。

【版权声明】:本站所有内容均来自网络,若无意侵犯到您的权利,请及时与我们联系将尽快删除相关内容!

发表回复