ARM指令系统的存储器操作模式是其高效执行的核心,涉及处理器工作模式、寻址机制、指令集及存储器管理单元的协同作用,直接影响数据访问效率与系统安全性,ARM架构通过多层次的存储器操作设计,既满足了高性能计算需求,又兼顾了嵌入式系统的实时性与安全性。

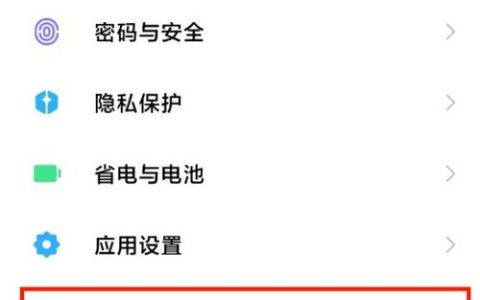

ARM处理器工作模式与存储器访问权限

ARM处理器支持7种工作模式,分为用户模式(User)和特权模式(System、FIQ、IRQ、SVC、Abort、Undefined),不同模式下,存储器访问权限存在显著差异:用户模式(USR)只能访问受限的虚拟地址空间,无法直接访问硬件控制寄存器;而特权模式(如SVC、FIQ)可访问全部物理地址,并能配置存储器管理单元(MMU)或保护单元(MPU),实现地址映射与权限控制,在SVC模式下,操作系统可通过修改页表或MPU寄存器,限制用户模式对特定存储区域的读写权限,防止非法访问,异常模式(如Abort)用于处理存储器访问错误(如缺页或权限违规),通过切换模式触发异常处理流程,确保系统稳定性。

存储器寻址方式:灵活访问的基础

ARM指令系统支持9种寻址方式,通过不同组合实现高效存储器访问,是存储器操作模式的核心组成部分,以下是关键寻址方式的详细说明:

| 寻址方式 | 格式 | 说明 | 示例 |

|---|---|---|---|

| 立即数寻址 | ADD Rd, Rn, #imm | 操作数为常数,直接编码在指令中 | ADD R0, R1, #0x10(R0=R1+16) |

| 寄存器寻址 | MOV Rd, Rm | 操作数在寄存器中,访问速度快 | MOV R2, R3(R2=R3) |

| 寄存器移位寻址 | ADD Rd, Rn, Rm, shift | 寄存器值经移位(如LSL、ASR)后参与运算 | ADD R4, R5, R6, LSL #2(R4=R5+R6×4) |

| 寄存器间接寻址 | LDR Rd, [Rn] | 寄存器值为存储器地址,通过该地址访问数据 | LDR R0, [R1](加载R1地址处的数据到R0) |

| 基址变址寻址 | LDR Rd, [Rn, #±imm] | 基址寄存器Rn±偏移量作为地址,支持前变址或后变址(如[Rn], #4) | LDR R2, [R3, #8](R3+8地址的数据到R2) |

| 多寄存器寻址 | LDM/STM Rn!, {Rlist} | 一次加载/存储多个寄存器,支持自动更新基址寄存器(表示回写) | LDMFD SP!, {R4-R7}(从堆栈恢复R4-R7) |

| 堆栈寻址 | PUSH/POP {Rlist} | 基于堆栈指针(SP)的自动增减寻址,用于函数调用/返回 | PUSH {R0, R1}(R0、R1入栈) |

| 块复制寻址 | LDMIA/STMIA Rn!, {Rlist} | 批量加载/存储,地址递增(IA)或递减(DB),适用于数据块传输 | STMIA R0!, {R2-R5}(将R2-R5存储到R0递增地址) |

| 相对寻址 | B label | 当前PC值加上偏移量作为目标地址,用于分支指令 | B loop(跳转到loop标签) |

存储器访问指令类型:数据流动的载体

ARM指令系统通过加载(Load)、存储(Store)及其变型指令实现存储器与寄存器间的数据传输,核心指令包括:

- LDR/STR指令:基础加载/存储指令,支持字节(B)、半字(H)、字(W)操作。

LDRB加载8位字节,STRH存储16位半字,且可通过U选项(无符号)或S选项(有符号符号扩展)处理数据类型差异。 - 批量加载/存储指令(LDM/STM):用于上下文切换或数据块传输,支持多种地址模式(如IA、DB、FD等)。

LDMFD(满递减堆栈)常用于函数返回时恢复寄存器,STMIA(递增后变址)适合连续数据存储。 - 堆栈操作指令(PUSH/POP):语法糖,对应

STMDB和LDMIA,自动处理SP指针调整,简化函数调用/返回流程。 - 特权指令:如

MCR/MRC,用于在特权模式下访问MMU/MPU寄存器,配置存储器属性(如缓存策略、权限位)。

存储器管理单元(MMU)与保护单元(MPU)

MMU是ARM存储器操作模式的高级特性,通过虚拟地址(VA)到物理地址(PA)的转换,实现内存隔离与共享,其核心功能包括:

- 地址映射:通过页表(两级或三级)将VA转换为PA,支持1MB-4KB大小的页/块映射。

- 权限控制:定义域(Domain)和访问权限(AP)位,限制用户模式对特定区域的读写/执行权限(如AP[1:0]=11表示用户模式可读可写)。

- 缓存属性:通过类型字段(如TEX、C、B)配置存储区域的缓存策略(Write-Through、Write-Back)、写缓冲使能及共享属性。

对于无MMU的嵌入式系统,MPU提供简化保护机制,通过定义6-8个存储器区域(基地址、大小、权限位),实现关键代码/数据的访问隔离。

缓存与写缓冲:优化存储器性能

为弥补存储器访问与CPU处理速度的差距,ARM采用缓存(Cache)与写缓冲(Write Buffer)机制:

- I-Cache/D-Cache:分别缓存指令和数据,减少访问主存延迟,Cache一致性通过MESI协议维护,确保多核/设备间数据同步。

- 写缓冲:暂存写操作数据,允许CPU在数据写入主存前继续执行后续指令,提升写性能,通过数据同步屏障(DSB)确保写操作完成。

字节序与存储器屏障

ARM支持小端(Little-Endian,最低有效字节在低地址)和大端(Big-Endian,最高有效字节在低地址)模式,通过系统控制寄存器(SCTLR)配置,影响多字节数据的存储顺序。

存储器屏障指令(DMB、DSB、ISB)用于强制内存访问顺序:

- DMB:确保数据内存访问顺序,防止指令重排导致的竞态条件。

- DSB:等待所有内存操作完成,确保后续指令依赖的数据已就绪。

- ISB:清空流水线,重新取指,确保后续指令从更新后的内存状态执行。

ARM指令系统的存储器操作模式通过多模式权限控制、灵活寻址机制、MMU/MPU保护及缓存优化,实现了高效、安全的存储器访问,从底层硬件(如MMU、Cache)到上层指令集(如LDM、PUSH),各层次协同工作,既满足了高性能计算场景的需求,又为嵌入式系统提供了实时性与可靠性的保障。

FAQs

Q1:ARM中LDR和STR指令的主要区别是什么?

A:LDR(Load Register)是加载指令,用于从存储器读取数据到寄存器;STR(Store Register)是存储指令,用于将寄存器数据写入存储器,核心区别在于数据传输方向:LDR实现“存储器→寄存器”,STR实现“寄存器→存储器”,LDR支持更多选项(如回写、变址模式[Rn, #±imm]),而STR主要用于数据存储,变址模式相对简单。

Q2:为什么ARM系统中需要存储器屏障指令?

A:由于CPU流水线、缓存和写缓冲的存在,内存访问顺序可能与程序顺序不一致(如写操作未立即生效、指令重排),存储器屏障指令(DMB/DSB/ISB)用于强制按指定顺序执行内存操作:DMB确保内存访问顺序,避免多线程数据竞争;DSB等待所有内存操作完成,确保依赖数据就绪;ISB清空流水线,确保指令从更新后的内存状态执行,这些指令对多核系统、设备驱动开发及关键数据同步场景至关重要。

【版权声明】:本站所有内容均来自网络,若无意侵犯到您的权利,请及时与我们联系将尽快删除相关内容!

发表回复