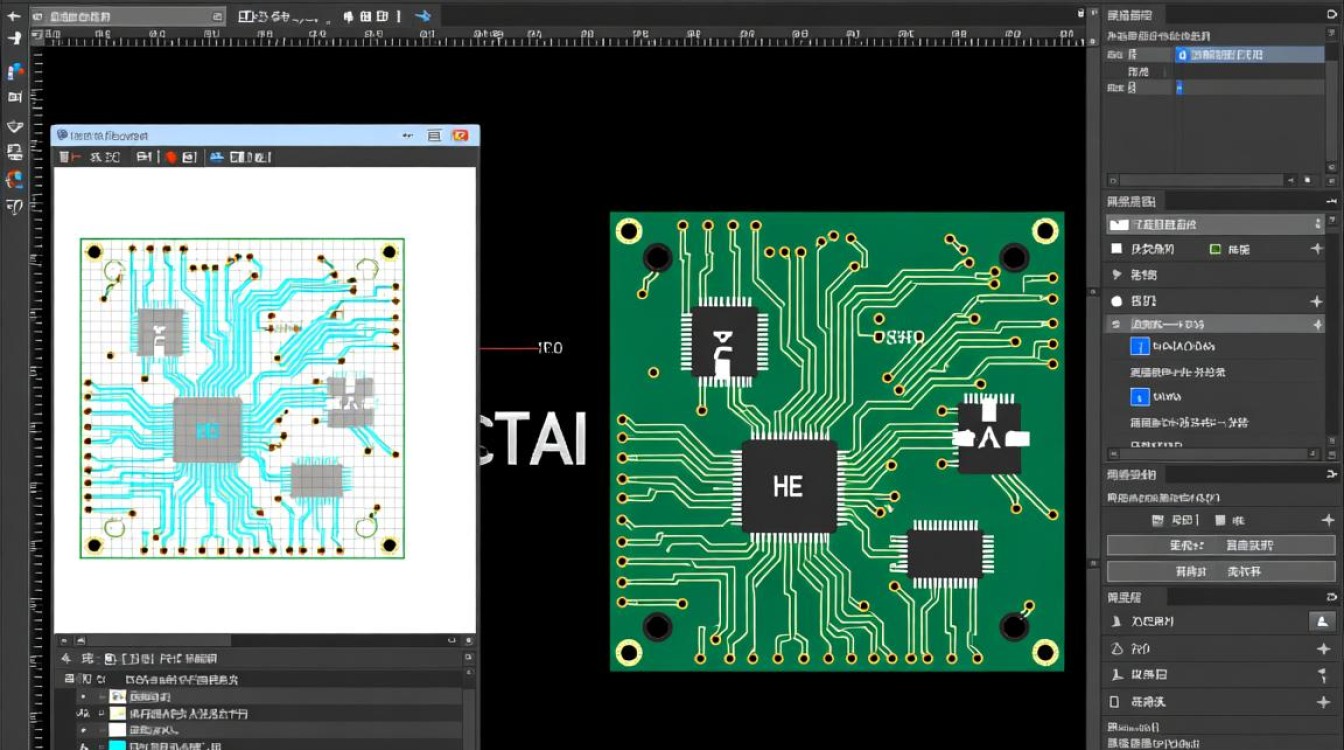

在使用Altium Designer(AD)进行PCB设计时,从原理图向PCB传递设计数据是至关重要的一步,这一过程并非总是一帆风顺,各种报错信息常常让初学者甚至经验丰富的工程师感到困扰,这些错误通常源于原理图设计、元件库管理或设计同步过程中的不一致,本文将系统地剖析AD生成PCB时的常见报错,并提供清晰的排查思路与解决方案。

元件封装缺失或不匹配

这是最常见的一类错误,当您执行“Design » Update PCB Document”命令时,系统在生成ECO(工程变更单)前会检查每个原理图元件是否都指定了有效的PCB封装。

错误表现:

- 在“Engineering Change Order”对话框中,变更项显示为红色错误,提示信息可能为“Failed to Match”、“Unknown Pin”或“Footprint Not Found”。

原因分析:

- 未指定封装: 原理图元件的属性中,Footprint字段为空。

- 封装名称错误: 指定的封装名称与PCB库中实际存在的封装名称不一致,可能存在拼写、大小写或多余空格的差异。

- 库路径问题: 封装所在的PCB库未被添加到当前项目中,或库文件路径无效。

排查方法:

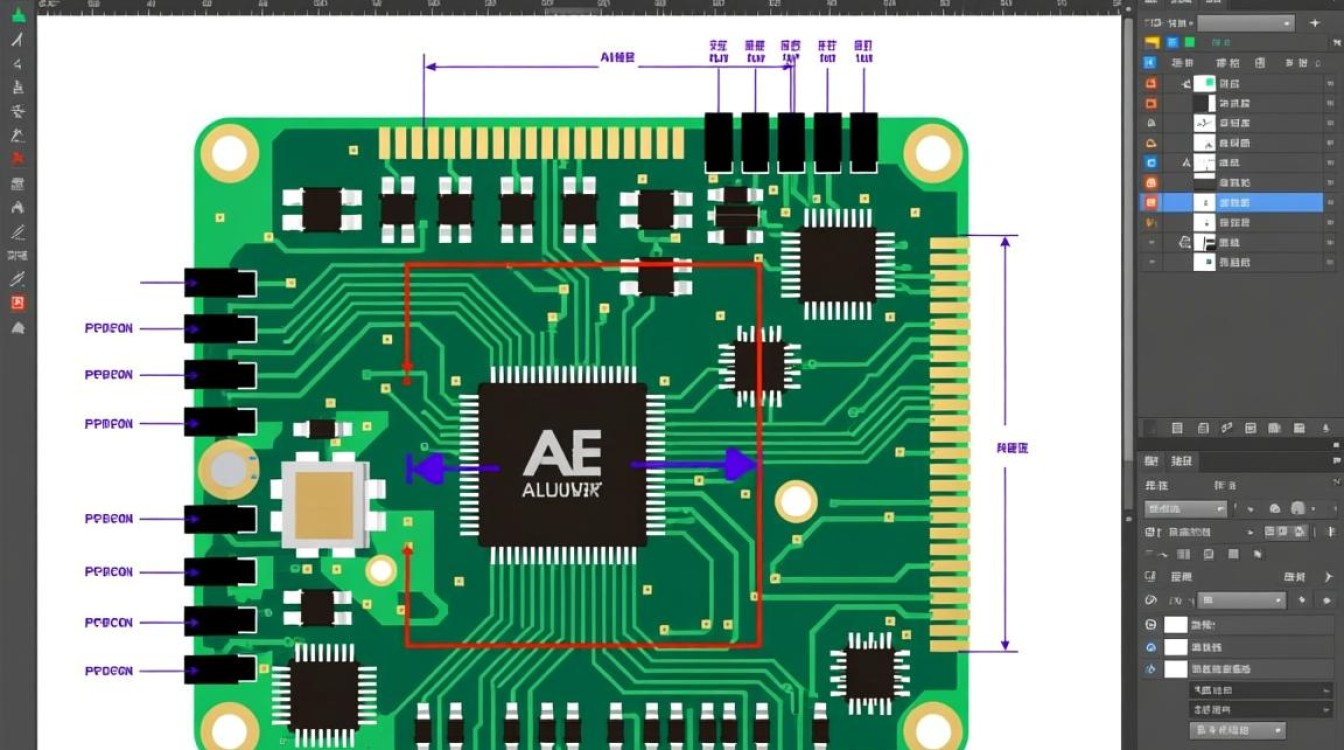

- 单个检查: 回到原理图,双击报错的元件,在“Properties”面板中检查“Footprint”区域,确认封装名称准确无误。

- 批量管理: 使用“Tools » Footprint Manager”工具,这是一个强大的管理界面,可以清晰地列出项目中所有元件的封装状态,快速定位缺失、无效或重复的封装,并进行统一修正。

- 检查库可用性: 确认包含所需封装的PCB库(.PcbLib文件)已经通过“Projects » Add Existing to Project…”添加到项目中,或者该库已安装在AD的库路径下并处于可用状态。

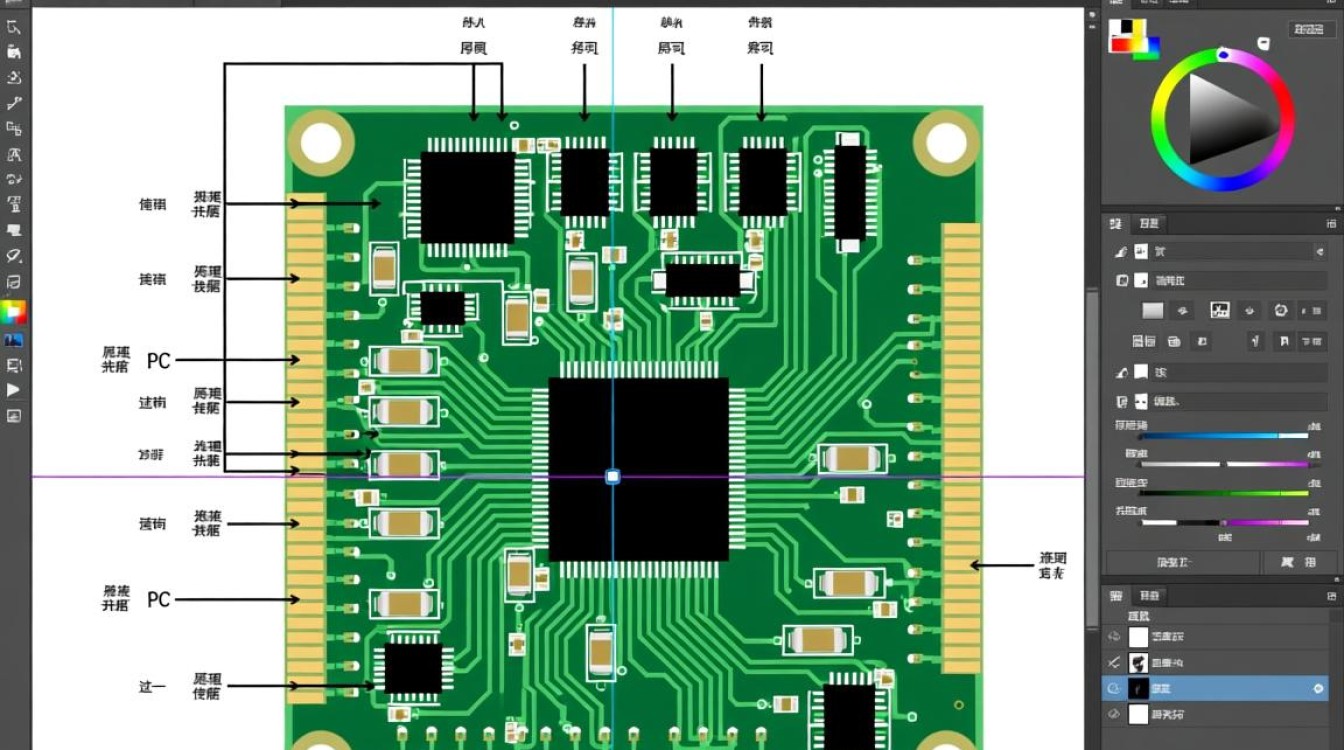

原理图设计内在错误

在同步数据之前,必须确保原理图本身是“干净”且无逻辑错误的,AD的编译功能是发现这类问题的利器。

错误表现:

- 执行“Project » Compile PCB Project”后,“Messages”面板弹出大量错误或警告。

- 常见的错误信息包括“Duplicate Part Designators”(元件标号重复)、“Net has only one pin”(网络只有一个引脚)、“Off Grid Object”(对象不在栅格上)等。

原因分析:

- 标号重复: 最典型的错误,例如两个电阻都被命名为R1,这在PCB中是无法区分的。

- 悬空引脚: 导线看似连接到元件引脚,但实际上并未连接到引脚的电气热点(Hotspot),导致该引脚网络不完整。

排查方法:

- 定期编译: 养成在同步前随时编译项目的习惯。“Project » Compile PCB Project”会执行电气规则检查(ERC),所有问题都会在“Messages”面板中列出。

- 定位错误: 双击“Messages”面板中的错误信息,AD会自动跳转到原理图中对应的违规对象,方便直接修改。

- 自动重排标号: 对于标号重复问题,可以使用“Tools » Annotation » Annotate Schematics”工具进行快速、有序的重新标注。

网络连接与ECO执行问题

即使原理图和封装都正确,ECO的执行过程也可能出现问题。

错误表现:

- 在“Engineering Change Order”对话框中点击“Execute Changes”后,部分操作失败(显示红色叉号)。

原因分析:

- 引脚映射不匹配: 原理图符号的引脚号与PCB封装的焊盘标识符不匹配,原理图中二极管引脚为A和K,而PCB封装焊盘为1和2,系统无法建立连接。

- 设计规则冲突: 在某些情况下,PCB中已有的设计(如固定网络)与ECO要添加的新网络产生根本性冲突。

排查方法:

- 仔细检查ECO: 在执行前,仔细审查ECO列表中的每一项变更,系统会给出状态提示,如“Added”、“Modified”或错误提示。

- 核对引脚映射: 对于报错的元件,同时打开其原理图符号(.SchLib)和PCB封装(.PcbLib),确保引脚号与焊盘标识符一一对应且完全相同。

- 部分执行: 如果只有少数几项出错,可以取消勾选这些错误项,先执行正确的变更,然后再集中精力解决那些顽固的错误。

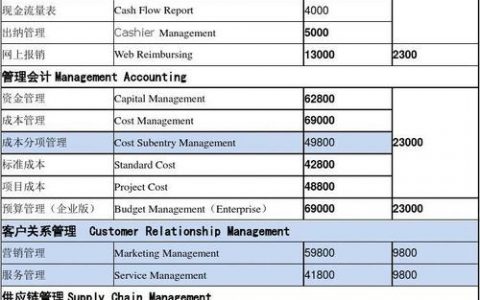

下表小编总结了常见报错类型及应对策略:

| 错误类型 | 常见提示信息 | 主要原因 | 排查方法 |

|---|---|---|---|

| 封装问题 | Failed to Match, Unknown Pin | 原理图符号与PCB封装链接错误或封装不存在 | 检查元件属性中的Footprint,使用封装管理器 |

| 标号重复 | Duplicate Part Designators | 多个元件使用了相同的唯一标识符(如R1, C1) | 编译项目,在Messages面板中查找并修改 |

| 网络问题 | Nets with only one pin, Unconnected objects | 原理图中导线未真正连接到引脚,或网络标签错误 | 检查连线连接点,使用编译功能查错,仔细核对ECO |

相关问答FAQs

问1:ECO执行时提示“Unknown Pin”或“引脚未连接”,但封装已经正确指定了,这是什么原因?

答:这个问题通常指向原理图符号与PCB封装之间的引脚映射不匹配,原理图库中的每个引脚都有一个唯一的“Designator”(如1, 2, A, K),PCB库中的每个焊盘也有一个“Designator”,在同步时,AD通过匹配这两个Designator来建立电气连接,请打开对应的原理图库文件和PCB库文件,仔细比较元件的引脚号和封装的焊盘标识符是否完全一致(注意大小写和是否有空格),确保它们能够一一对应。

问2:为什么明明封装库中有这个封装,系统还是会报错“Failed to Match”?

答:这种情况通常是由于“名称不匹配”导致的细微错误,请检查以下几点:1)拼写和大小写:AD的匹配是区分大小写的,“SOIC-8”和“Soic-8”被视为两个不同的封装,2)多余空格:封装名称前后或中间可能存在不易察觉的空格,3)库的可用性:确认该封装所在的PCB库确实已经被当前项目所引用,最可靠的方法是,在原理图元件的属性界面,点击Footprint字段旁的“…”按钮,从可用的库列表中直接选择封装,而不是手动输入,这样可以避免所有拼写和格式错误。

【版权声明】:本站所有内容均来自网络,若无意侵犯到您的权利,请及时与我们联系将尽快删除相关内容!

发表回复